“工欲善其事,必先利其器”,熟练使用Allegro软件对PCB Layout工程师来说是至关重要的。本文,板儿妹将和大家分享10条非常实用的Allegro实操技巧,希望对大家的工作有所帮助。

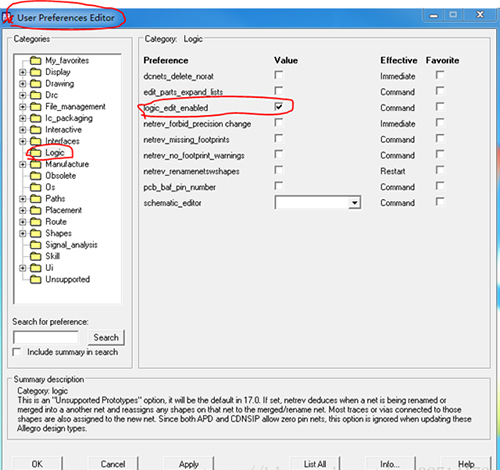

修改Pin脚网络

set up --user preference Editor

Logic--net logic

Option处选择网络,然后find处选择Pins,之后点击要修改网络的Pin即可将原来的网络修改为所选择的网络。

如何加入不同的via?

1) 用Allegro Utilities->Pad stack工具制作

2) Setup-->constraints...-->Physical (lines/vias)rule set中的Set values...按钮Name栏输入via名Add之即可(注意顶上Constraint Set Name和Subclass)

如何让Allegro显示实心焊盘?

Setup-->Drawing Options... Display: Filled pads and Display drill holes

如何只显示一部分飞线?

在实际Layout中常常希望只显示出一部分Net的飞线,可以通过Display-->Show Rats,看清它们的相对位置,方便布线。

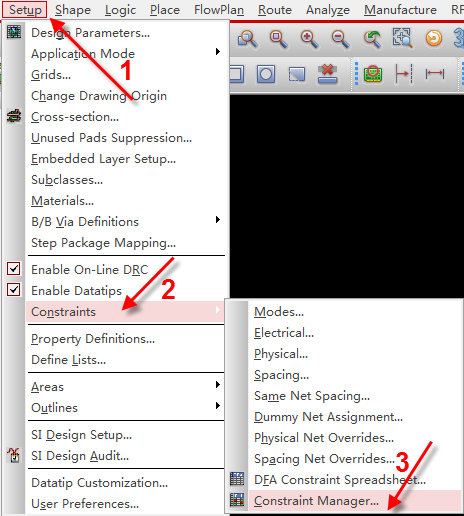

allegro软件的绝对传输延迟怎么设置?

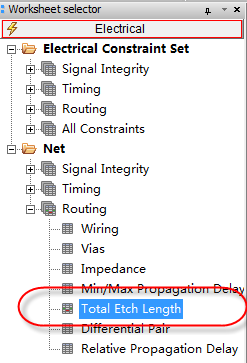

第一步,打开规则管理器,执行菜单命令Setup-Constraints,在下拉菜单中选择Constraint Manager,如图5-90所示,进入到规则管理器中;

图5-90 规则管理器示意图

第二步,进入规则管理器以后,在CM左侧的目录栏中选择Net,在Routing中选择Total Etch Length,如图5-91所示,设置信号的线的总长度;

图5-91 设置绝对长度示意图

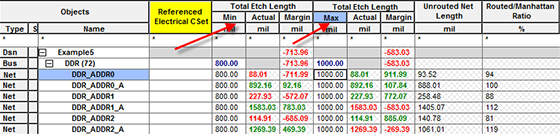

第三步,进入到右边栏,对需要做等长的信号线,创建好Bus,在Total Etch Length中输入最小值、最大值即可,如图5-92所示,每一组的信号线都会跟这个对比产生相对应的误差,按这个误差做等长即可;

图5-92 设置绝对长度最大值最小值示意图

第四步,回到PCB界面,如果需要做等长的信号线没有满足最小值或者最大值的要求,都会报相对应的DRC错误,用于提醒工程师做等长设计。

allegro中,如何实现器件移动时,走线不断开?

1、首先点击左上角placementedit 模式按钮

2、在右边的find中将symbols勾选

3、随后点击move按钮

4、在右侧options中勾选slide etch(平滑电气连接)

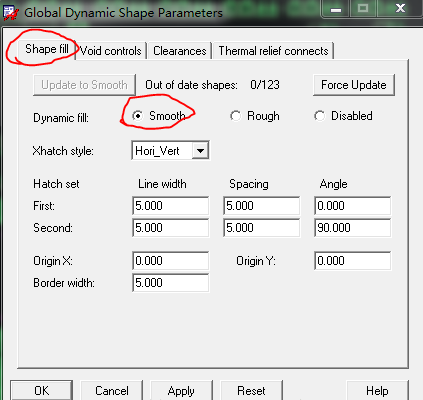

铜皮不能自动更新

铜皮属性是dynamic copper,但是修改的过程中他不会自动更新。可以选择shape--global dynamic shape parameters(这边改动之后所有铜皮都会修改为相应的设置)

将dynamic fill设置为smooth即可。

修改Shape属性的outline

首先关闭其他东西,直留一个outline。

然后shape--decompose shape,在option那边选择board geometry --outline。

最后框选住整个outline就会变成board geometry属性的outline了。

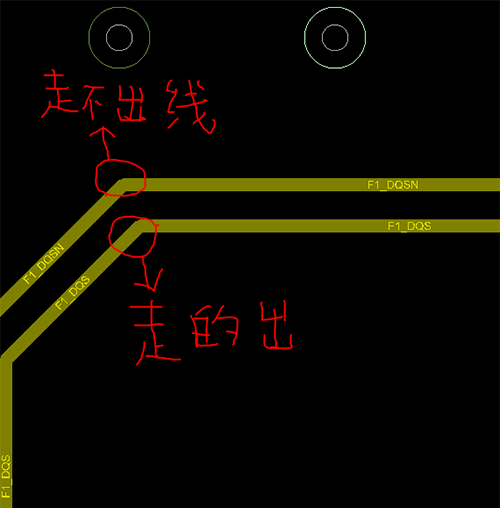

调整差分线

调整差分线的时候,即用连线命令在差分线拐角位置开始走线,外围的那根线会有走不出来的情况。这是因为拐角外围的那个点内围没有与他平行的点,但是内围的线在外围有对应的平行点,所以内围那根线可以走出线。

除此之外,option那边的bubble必须设置为off。不然也是不行的。

删除dangling线

route——Gloss—–parameters

弹出选项窗口点 line smoothing 这一任务项,然后ok,然后点gloss即可消除dangling线。

(图文内容整理自网络)

抗“疫”时期,学习不能停。在疫情结束之前,快点学院将联合腾讯课堂,持续开放部分课程供大家免费在线学习!

↓↓↓