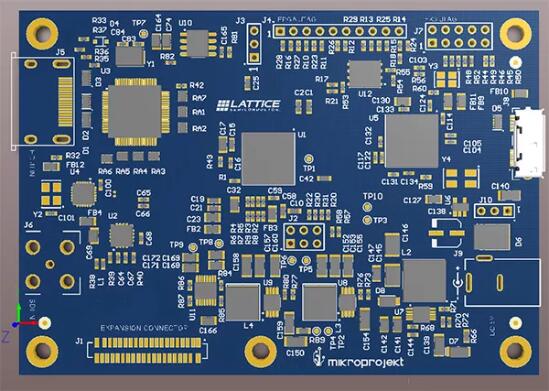

布局和布线是PCB设计中最重要的两个环节,工程师在遵循信号质量、DFM、EMC等规则要求完成PCB的布局、布线后,还需要对相关的内容进行检查。

布局检查

在PCB设计中,合理的布局是PCB设计成功的第一步,因此在布局完成后需要严格检查以下内容:

1、 PCB尺寸标记,器件布局是否和结构图纸一致,是否符合PCB制造工艺要求,如最小孔径最小线宽。

2、元器件之间在二维、三维空间上是否相互干涉,是否会与结构外壳相互干涉。

3、元器件是否全部放置完毕。

4、需要经常插拔或者更换的元器件是否方便插拔与更换。

5、热敏器件与发热元器件是否有合适的距离。

6、调整可调器件和按下按键是否方便。

7、安装散热器的位置是否空气通畅。

8、信号流向是否通畅且互联最短。

9、线路干扰问题是否有考虑。

10、插头、插座是否与机械设计矛盾。

布线检查

布线是整个PCB设计中最重要的工序,这将直接影响着PCB板的性能好坏。在完成PCB布线后,工程师需要对数模、时钟和高速部分、电源和地等进行检查。

一、数模

1、数字电路和模拟电路的走线是否已分开,信号流是否合理

2、A/D、D/A以及类似的电路如果分割了地,那么电路之间的信号线是否从两地之间的桥接点上走(差分线例外)?

3、必须跨越分割电源之间间隙的信号线应参考完整的地平面。

4、如果采用地层设计分区不分割方式,要确保数字信号和模拟信号分区布线。

二、时钟和高速部分

1、高速信号线的阻抗各层是否保持一致

2、高速差分信号线和类似信号线,是否等长、对称、就近平行地走线?

3、确认时钟线尽量走在内层

4、确认时钟线、高速线、复位线及其它强辐射或敏感线路是否已尽量按3W原则布线

5、时钟、中断、复位信号、百兆/千兆以太网、高速信号上是否没有分叉的测试点?

6、LVDS等低电平信号与TTL/CMOS信号之间是否尽量满足了10H(H为信号线距参考平面的高度)?

7、时钟线以及高速信号线是否避免穿越密集通孔过孔区域或器件引脚间走线?

8、时钟线是否已满足(SI约束)要求

9、差分对、高速信号线、各类BUS是否已满足(SI约束)要求

三、电源和地

1、如果电源/地平面有分割,尽量避免分割开的参考平面上有高速信号的跨越。

2、确认电源、地能承载足够的电流。过孔数量是否满足承载要求(估算方法:外层铜厚1oz时1A/mm线宽,内层0.5A/mm线宽,短线电流加倍)

3、对于有特殊要求的电源,是否满足了压降的要求

4、为降低平面的边缘辐射效应,在电源层与地层间要尽量满足20H原则。(条件允许的话,电源层的缩进得越多越好)。

5、如果存在地分割,分割的地是否不构成环路?

6、相邻层不同的电源平面是否避免了交叠放置?

7、保护地、-48V地及GND的隔离是否大于2mm?

8、-48V地是否只是-48V的信号回流,没有汇接到其他地?如果做不到请在备注栏说明原因。

9、靠近带连接器面板处是否布10~20mm的保护地,并用双排交错孔将各层相连?

10、电源线与其他信号线间距是否距离满足安规要求?

四、禁布区

1、金属壳体器件和散热器件下,不应有可能引起短路的走线、铜皮和过孔

2、安装螺钉或垫圈的周围不应有可能引起短路的走线、铜皮和过孔;螺钉孔按照星月孔设计;周围禁布距离满足20mil以上

3、设计要求中预留位置是否有走线

4、非金属化孔内层离线路及铜箔间距应大于0.5mm(20mil),外层0.3mm(12mil)

单板起拔扳手轴孔内层离线路及铜箔间距应大于2mm(80mil)

5、铜皮和线到板边 推荐为大于2mm 最小为0.5mm

6、内层地层铜皮到板边 1 ~ 2 mm,最小为0.5mm

(内容整理自网络)

想扩充和提升自己硬件方面的技能吗?想在职场上提升自己的竞争力吗?不妨从学习原理图设计开始。扫描(识别)以下二维码,可在“腾讯课堂”学习Orcad原理图设计实战课程:《4周通过VR学习原理图设计》。

▲扫码试听《4周通过VR学习原理图设计》课程