PCB上的走线到底能不能走90°拐角?这是一个老生常谈的问题,也是让很多新入坑的PCB Layout 工程师疑惑的问题。今天,我们不妨一起来聊聊这个话题。

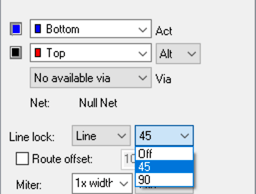

很多IC原厂的PCB设计指南手册上都有单独的章节专门指出:“对于关键的高速信号线,走线不能以90°拐角,必须以两个135°角来实现,在PCB Layout软件里就是选择45°走线模式。”

为什么会有这样的规定?90°拐角会对信号质量带来负面影响吗?答案是肯定的。不过这个影响到底有多严重,那是要看条件的。

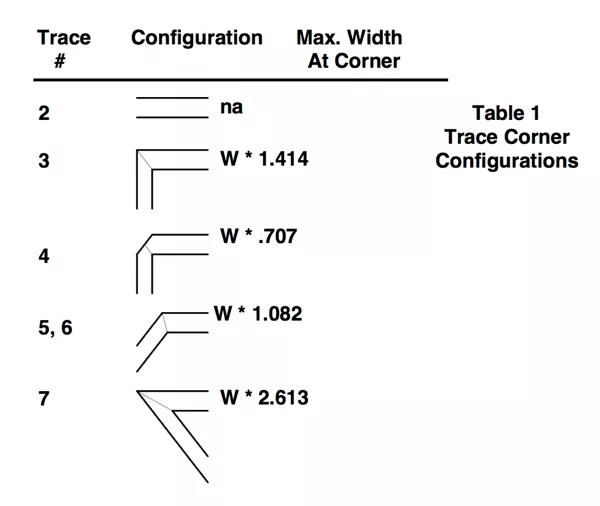

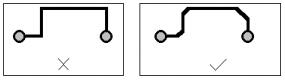

90°拐角走线之所以会产生信号完整性问题。原因在于,由于传输线直角拐角部分的铜箔宽度比直线走线的铜箔宽度要宽一些,会造成直角折弯处的特性阻抗突变,这对于普通信号走线并不会造成问题,但对于高速传输线来说,则会带来信号的反射,反射严重的话会造成信号完整性问题。

我们知道,在设计高速电路板时,要注意特性阻抗的变化,特性阻抗变化会带来信号的反射,使得信号质量变差。通过45°的拐角模式走线而不是以90°模式进行拐角,在拐角处铜箔宽度突变会更少一些,可以减少由于布线宽度的变化而引起的信号反射和这个额外的离散电容造成的信号上升时延的改变。

而对于PCB走线的要求,一些公司内部的PCB设计规范也有说明。

PCB布线处理的基本要求

1) 规则驱动布线时,保证规则的合理性,使用并提供过程Do文件;

2) 过孔、线宽、安全间距避免采用极限值。

3) 规则驱动布线的过程中尽可能考虑ICT测试点设计;

4) 管脚引线尽可能从PIN中心引出;

5) 信号线与PIN间尽可能拉开距离;

6) 无通孔或机械盲孔上焊盘;

7) 走线到板边的距离通常情况下需≥2mm,在不能满足条件的情况下,至少保证不小于20mil;

8) 表面除短的互连线和Fanout的短线外,信号线尽可能布在内层;

9) 金属外壳器件下,不允许有过孔、表层走线;

10) 尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。采用屏蔽和加大安全间距等方法,保证信号质量;

11) 电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号线;

12) 有阻抗控制要求的网络应布置在阻抗控制层上;

13) 布线尽可能靠近一个平面,并避免跨分割。若必须跨分割或者无法靠近电源地平面,这些情况仅允许在低速信号线中存在;

14) 高速信号线区域相应的电源平面或地平面尽可能保持完整;

15) 平面层和布线层分布对称,介质厚度分布对称,过孔跨层保持对称;

16) 平面层分割避免出现直角或锐角;

17) 大面积敷铜时参考网络采用地网络;

18) 敷铜时避免出现直角或锐角,并且上下铜皮须有过孔相连,尤其在铜皮的边缘处,边缘相邻过孔相距约200~400mils;

19) 布线保持均匀,大面积无布线的区域需要敷铜,但要求不影响阻抗控制;

20) 布线无DRC错误,无同名网络错误;

21) 所有信号线必须倒角,倒角角度为45度,特殊情况除外;

倒角规则

PCB设计中应避免产生锐角和直角,产生不必要的辐射,同时工艺性能也不好。

22) PCB设计完成后无未布完的网络,且PCB网表与原理图网表一致。

建议:在进行PCB Layout时,一律禁止出现直角,无论是普通的信号线还是高速数字信号传输线还是RF传输线,包括覆铜的铜皮,一律修成钝角。

(来源:整理自吴川斌的博客、某500强公司内部PCB设计规范)

想扩充和提升自己硬件方面的技能吗?想在职场上提升自己的竞争力吗?不妨从学习原理图设计开始,扫描(识别)以下二维码可在“腾讯课堂”学习Orcad原理图设计实战课程:《4周通过VR学习原理图设计》。

▲扫码试听《4周通过VR学习原理图设计》课程