去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。在PCB设计时,工程师需要特别注意去耦电容的摆放。

去耦电容VS旁路电容

在电子电路中,去耦电容和旁路电容都是起到抗干扰的作用,电容所处的位置不同,称呼就不一样了。对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除,而去耦(decoupling)电容也称退耦电容,是把输出信号的干扰作为滤除对象。去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。

PCB设计时去耦电容的摆放

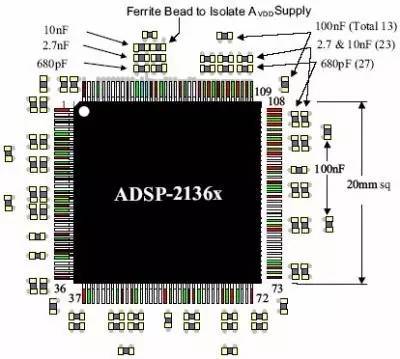

对于电容的安装,首先要提到的就是安装距离。容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置。容值稍大些的可以距离稍远,最外层放置容值最大的。但是,所有对该芯片去耦的电容都尽量靠近芯片。

下图就是一个摆放位置的例子。本例中的电容等级大致遵循10倍等级关系。

还有一点要注意,在放置时,最好均匀分布在芯片的四周,对每一个容值等级都要这样。通常芯片在设计的时候就考虑到了电源和地引脚的排列位置,一般都是均匀分布在芯片的四个边上的。因此,电压扰动在芯片的四周都存在,去耦也必须对整个芯片所在区域均匀去耦。如果把上图中的680pF电容都放在芯片的上部,由于存在去耦半径问题,那么就不能对芯片下部的电压扰动很好的去耦。

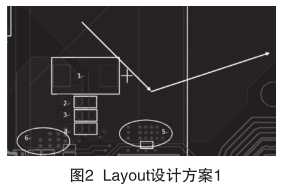

设计方案1分析

如图2所示为Layout设计方案1,其中箭头所示为电源传输路径的方向,1、2、3、4为去耦电容,5为电容的电源孔,6为电容的地孔。因负载芯片端没有足够的空间放置电容,所以去耦电容1、2、3、4放到了传输路径的中间位置,并遵循传统设计规则,电容都放在了与芯片相同的层面TOP层。因此处高速线密集,只有在5和6的位置有打过孔的空间。

根据PCB寄生电感公式,计算电容1的PCB寄生电感(包含电源和地电感两部分)约为0.14 nH,电容2的PCB寄生电感约为0.112 nH。

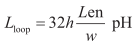

▲PCB寄生电感公式

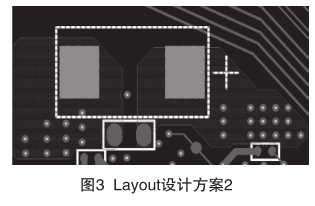

设计方案2分析

设计方案2如图3所示,其将电容1和2放到了距离过孔更近的BOT层,电容3和4的位置不变。对电容1和2来说,因其距离过孔位置更近,其PCB寄生电感将会相应减小,但是因电容位置BOT层,也会带来额外的过孔寄生电感。

根据PCB寄生电感公式,计算电容1的PCB寄生电感约为0.09 nH,电容2的PCB寄生电感约为0.06 nH。

根据过孔寄生电感公式,电源过孔簇5带来的寄生电感约为0.013 nH,地过孔簇6带来的寄生电感约为0.017 nH。

▲过孔寄生电感公式

总体来看,方案2的寄生电感小于方案1,方案2的去耦设计会带来更好的去耦效果。

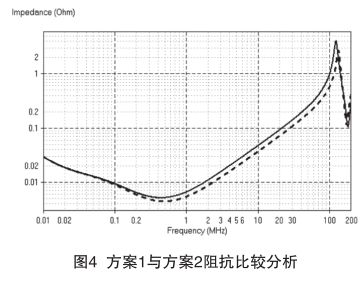

仿真验证

为了验证上述的理论分析的正确性,对方案1与方案2的设计进行仿真分析,其仿真结果如图4所示。其中实线为方案1的阻抗曲线,虚线为方案2的阻抗曲线。可以看到虚线所示的阻抗小于实线所示阻抗,且其主要区别位于寄生电感作用区域,从而验证了以上理论分析的正确性和优化方案2的设计可行性。

(图文整理自:CPCA印制电路信息 作者:上海交通大学 宋晓峰;硬件十万个为什么)

想扩充和提升自己硬件方面的技能吗?想在职场上提升自己的竞争力吗?不妨从学习原理图设计开始。扫描(识别)以下二维码,可在“腾讯课堂”学习Orcad原理图设计实战课程:《4周通过VR学习原理图设计》。

▲扫码试听《4周通过VR学习原理图设计》课程