上一期介绍了在PCB设计中HDA及IDE模块的的注意事项,本期继续分享时钟CLK和LAN网口在PCB设计中的注意事项:

九、 CLK Port

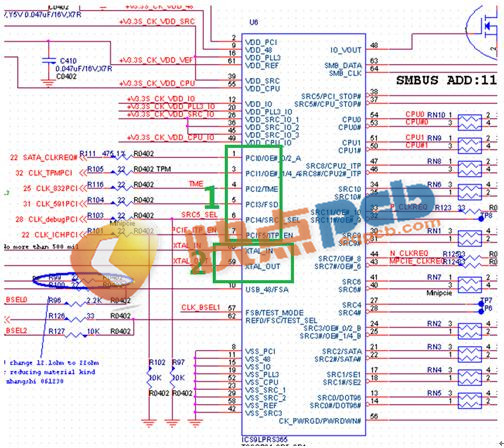

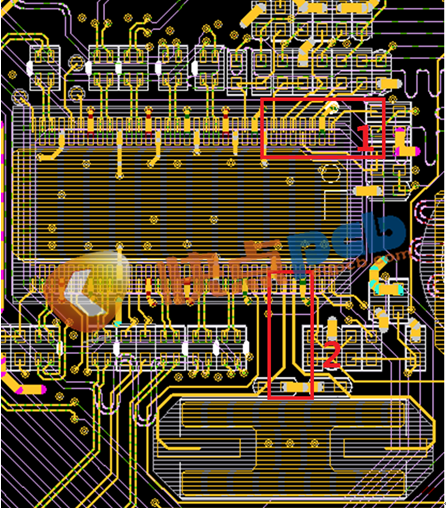

1)注意上图1号框中的PCI_CLK信号布线要求

2)注意上图2号框中的晶振的布线要求

1)上图1号框中的PCI_CLK信号在布线的时候需要做等长处理;

2)上图2号框中的晶振到芯片的走线长度不要超过500mil,长度尽量等长;

CLK分类:

1)Host Clock:MCH_BCLK(差分信号)和CPU_BCLK(差分信号),166/200MHZ

2)PCI_CLK:PCI_CLK【5:0】,33MHZ

3)REFCLK:14MHZ

4)USBCLK:48MHZ

5)DOTCLK:96MHZ

6)SRCCLK:(serial reference clock)100MHZ

CLK Port Layout基本注意事项:

Host Clk:

1)Clk芯片到电阻的走线长度要在500mil范围内;

2)差分信号布线时,与外界(VIA、Shape、Line、PAD)间距至少保持在20mil以上;

3)两对差分信号要保持等长,长度误差值要小于10mil;

33MHZ Clock (PCICLK):

1)PCICLK【5:0】需做等长处理;

2)PCICLK【4:0】做等长时要以PCICLK5为基准;

3)做等长时需要满足以下关系:

(1)PCICLK0 1.49” ―6.69”

(2)PCICLK1 0.36” ―5.56”

(3)PCICLK2 -0.77” ―4.43”

(4)PCICLK3 -1.90” ―3.30”

(5)PCICLK4 -3.03”―2.17

DOTCLK(DRECLK/#)

1)差分阻抗为100 Ohm;

2)分段等长误差25mil,总误差25mil;

SRC CLK

1)差分阻抗为100 Ohm,包括SATA、PCIE等的CLK信号;

2)单对信号分段等长误差控制在25mil范围内;

3)组内差分信号与差分信号之间无等长关系要求;

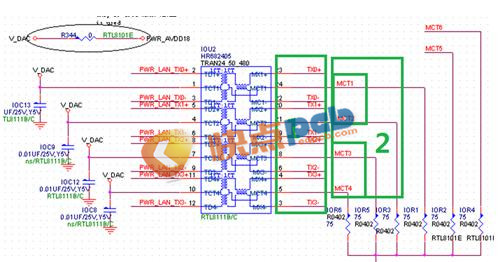

十、 LAN Port

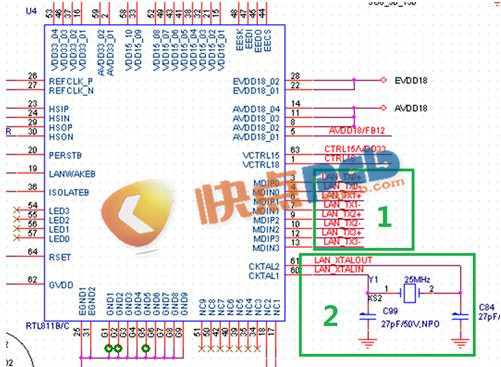

1)上图1号框中的四对信号布线时间距需要控制在50mil以上;并要做等长处理,长度误差值不允许超过5mil;

2)上图2号框中的晶振在布局时,要原理板边,IO口以及高速信号线;

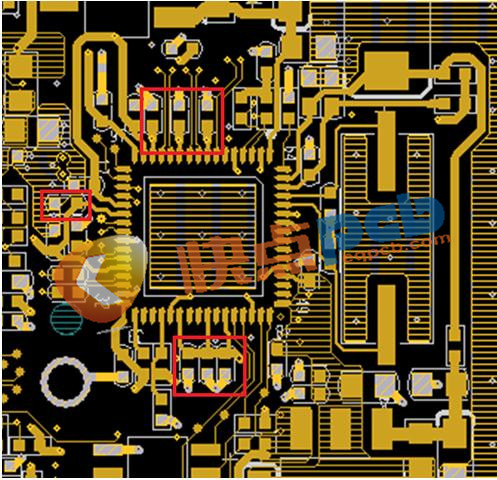

1)上图红色框中的去耦电容在PCB布局时需要尽量摆放在靠近PWR Pin的位置,布线的长度需要控制在200mil范围内;

1)上图1号框中的差分信号布线时需要尽量的远离板边,并且间距需要保持在50mil以上,同对等长时误差必须控制在5mil范围内;

2)上图2号框中的信号需要两两的作为差分信号处理;

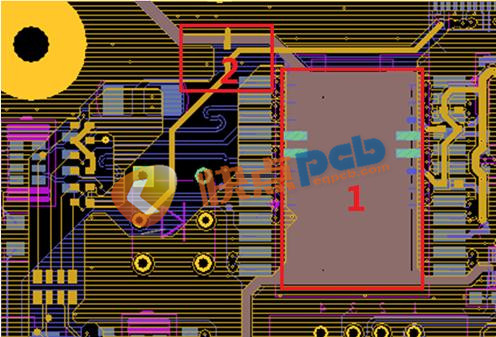

1)如上图1号框中所示,PCB设计中transformer中心所有层需要掏空处理;

2)数字区域与模拟区域分割线以60mil为最佳,且区域内器件及走线要严格区分;

更多PCB设计行业知识,可持续关注微信【快点PCB平台】公众号