可测性设计(DFT)是适应集成电路的发展的测试需求所出现的一种技术,主要任务是设计特定的测试电路,同时对被测试电路的结构进行调整,提高电路的可测性,即可控制性和可观察性。

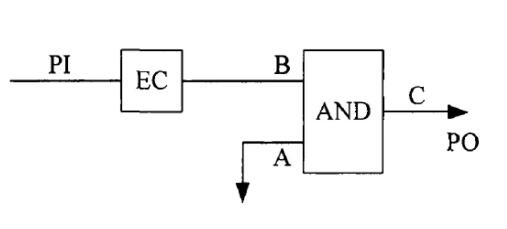

1、可控性:指的是是否可以从电路的初级输入控制内部引线逻辑状态。一条链路可以通过电路的初级输入端(PI)控制其状态,则这条链路称是可控制的,否则就是不可控制,见下图,二输入与门有两个输入端A和B,如果A直接接地,B是网络EC的输出信号。在这个电路中,无论初级输入端PI的值是什么,与门的输出端C始终为0,不可能为1,则C是1不可控的。

2、可观察性:指的是是否可以从电路的初级输出端或其他特殊的测试点观察电路内部引线逻辑状态。内部引线A的值可以通过某种方式传播到PO,在上图中,由于C的值始终为0,并且是由于A的值为0所致。因此在C位置就不能判断B点的逻辑值究竟是什么。假如C是电路唯一的PO,则内部引线B就是不可观察的。

按测试结构分,DFT目前比较成熟的技术主要有扫描设计(ATPG)、内建自测试(BIST)、边界扫描设计(BSCAN)等。其中ATPG用于测试芯片的数字逻辑电路,BIST多用于测试芯片的片上内存,BSCAN用于测试芯片的IO端口。

(图文整理自网络,版权归原作者所有。)

想通过教育培训扩充和提升自己硬件方面的技能吗?想在职场上提升自己的竞争力吗?不妨从学习原理图设计开始。扫描(识别)以下二维码,可在“腾讯课堂”学习Orcad原理图设计实战课程:《4周通过VR学习原理图设计》。

▲扫码试听《4周通过VR学习原理图设计》课程